Especificación

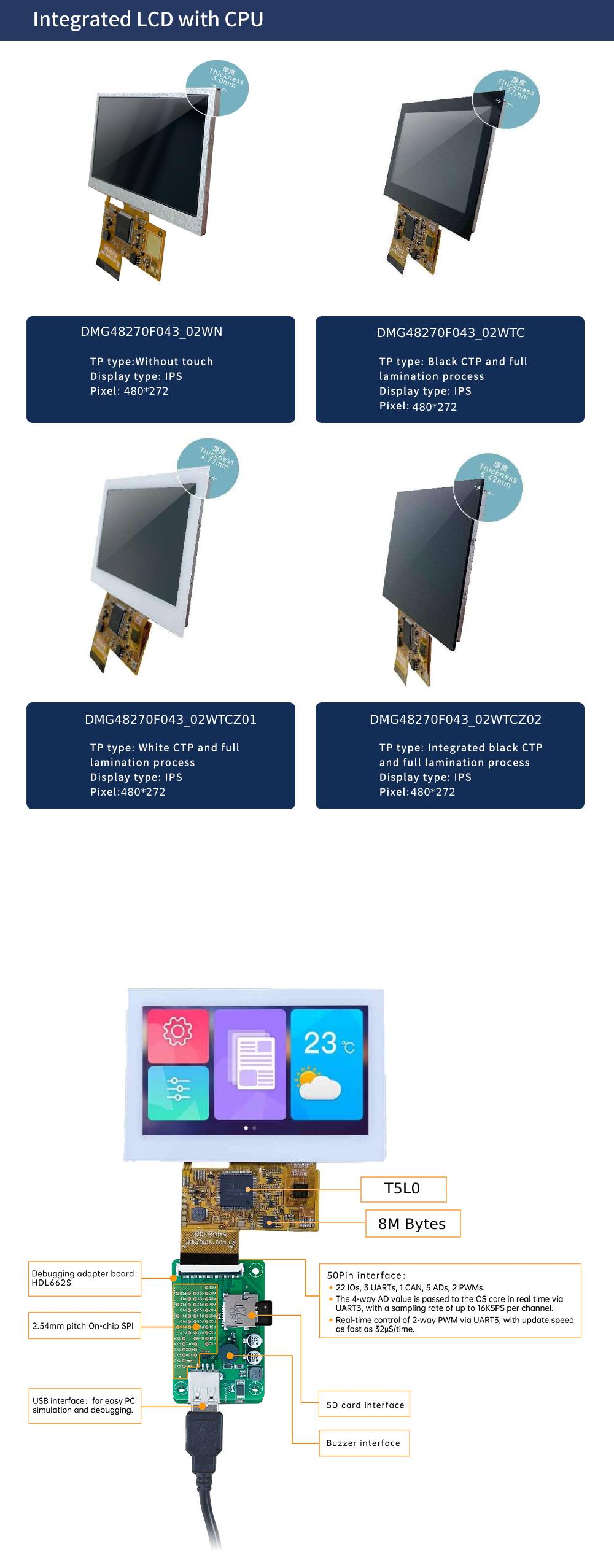

| Cor | 262K cores |

| Tipo LCD | IPS-TFT-LCD, |

| Ángulo de visión | Anxo de visión ampla, valor típico de 85°/85°/85°/85° (L/R/U/D) |

| Área activa (AA) | 95,04 mm (ancho) × 53,86 mm (alto) |

| Resolución | 480×272 |

| Retroiluminación | LED |

| Brillo | DMG48270F043_02WN:300nit |

| DMG48270F043_02WTR: 250 nit | |

| DMG48270F043_02WTC: 250 nit | |

| DMG48270F043_02WTCZ01:250nit | |

| DMG48270F043_02WTCZ02:50nit |

| Tensión de potencia | 3,6 ~ 5,5 V, valor típico de 5 V |

| Operación actual | VCC=5V, luz de fondo máxima, 220mA |

| VCC=5V, retroiluminación apagada, 100mA |

| Interface de usuario | 50Pin_0,5 mm FPC |

| Baudrate | 3150~3225600bps |

| Tensión de saída | Saída 1;3,0 ~ 3,3 V |

| Saída 0;0~0,3 V | |

| Tensión de entrada (RXD) | Entrada 1;3,3 V |

| Entrada 0;0 ~ 0,5 V | |

| Interface | UART2: TTL; |

| UART4: TTL;(Só dispoñible despois da configuración do SO) | |

| UART5: TTL; (Só dispoñible despois da configuración do SO | |

| Formato de datos | UART2: N81; |

| UART4: N81/E81/O81/N82;4 modos (configuración do SO) | |

| UART5: N81/E81/O81/N82;4 modos (configuración do SO) |

| Pin | Definición | E/S | Descrición funcional |

| 1 | +5 V | eu | Fonte de alimentación, DC3.6-5.5V |

| 2 | +5 V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | eu | ADC de 5 entradas.Resolución de 12 bits en caso de alimentación de 3,3 V.Tensión de entrada 0-3,3 V.Excepto AD6, os datos restantes envíanse ao núcleo do sistema operativo a través de UART3 en tempo real cunha frecuencia de mostraxe de 16 KHz.AD1 e AD5 pódense usar en paralelo, e AD3 e AD7 poden usarse en paralelo, o que equivale a dous AD de mostraxe de 32 KHz.AD1, AD3, AD5, AD7 poden usarse en paralelo, o que equivale a un AD de mostraxe de 64 KHz;os datos súmanse 1024 veces e despois divídense por 64 para obter un valor AD de 64 Hz de 16 bits mediante sobremostraxe. |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD2 | I | |

| 11 | +3.3 | O | Saída de 3,3 V, carga máxima de 150 mA. |

| 12 | SPK | O | MOSFET externo para conducir zumbador ou altofalante.A resistencia externa de 10K debe ser tirada cara ao chan para garantir ese acendido |

| 13 | SD_CD | E/S | Interface SD/SDHC, o SD_CK conecta un capacitor de 22pF a GND preto da interface da tarxeta SD. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | E/S | |

| 16 | SD_D2 | E/S | |

| 17 | SD_D1 | E/S | |

| 18 | SD_D0 | E/S | |

| 19 | PWM0 | O | 2 Saída PWM de 16 bits.A resistencia externa de 10K debe ser tirada cara ao chan para garantir que o encendido sexa de baixo nivel.O núcleo do sistema operativo pódese controlar en tempo real mediante UART3 |

| 20 | PWM1 | O | |

| 21 | P3.3 | E/S | Se se usa RX8130 ou SD2058 I2C RTC para conectarse a ambos IO, SCL debe estar conectado a P3.2 e SDA conectado a P3.3 en paralelo cunha resistencia de 10K pull-up a 3,3V. |

| 22 | P3.2 | E/S | |

| 23 | P3.1/EX1 | E/S | Pódese usar como unha entrada de interrupción externa 1 ao mesmo tempo e admite os modos de interrupción de nivel de baixa tensión ou de bordo posterior. |

| 24 | P3.0/EX0 | E/S | Pódese usar como entrada de interrupción externa 0 ao mesmo tempo e admite modos de interrupción de nivel de baixa tensión ou de bordo posterior. |

| 25 | P2.7 | E/S | Interface IO |

| 26 | P2.6 | E/S | Interface IO |

| 27 | P2.5 | E/S | Interface IO |

| 28 | P2.4 | E/S | Interface IO |

| 29 | P2.3 | E/S | Interface IO |

| 30 | P2.2 | E/S | Interface IO |

| 31 | P2.1 | E/S | Interface IO |

| 32 | P2.0 | E/S | Interface IO |

| 33 | P1.7 | E/S | Interface IO |

| 34 | P1.6 | E/S | Interface IO |

| 35 | P1.5 | E/S | Interface IO |

| 36 | P1.4 | E/S | Interface IO |

| 37 | P1.3 | E/S | Interface IO |

| 38 | P1.2 | E/S | Interface IO |

| 39 | P1.1 | E/S | Interface IO |

| 40 | P1.0 | E/S | Interface IO |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | E/S | Interface IO |

| 46 | P0.1 | E/S | Interface IO |

| 47 | CAN_TX | O | Interface CAN |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2 (porto serie UART0 do núcleo do sistema operativo) |

| 50 | UART2_RXD | I |

Modelo: HDW101_A5001L

Modelo: HDW215_002L